| (おまけ)FPGAでSFCコントローラを作る |

| 部屋の隅で埃をかぶっているDE0に活躍の機会を! |

|

|

| 背景 |

|

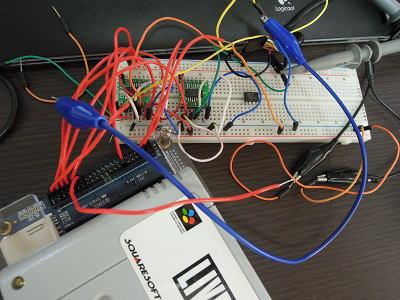

| シリアル通信で制御可能なSFCコントローラが大方出来たところで、勘が失われないうちに何か他に面白いことが出来ないかと考えてみたところ、部屋の隅で埃を被っているDE0を発見した。何年か前に少しいじったきりほとんどいじっていない。これはかわいそうだということでDE0でSFCコントローラを作ることにした。・・・と言ってもコントローラの仕組みは簡単なのでFPGAでシフトレジスタを実装するだけです。 |

|

|

コード(Verilog HDL)

|

module sfc(a,clk,load,q);

input [15:0] a;

input clk,load;

output q;

reg q;

reg [15:0] r;

always @(posedge clk or posedge load) begin

if(load)

begin

r = a;

q = r[15];

r = r << 1;

end

else

begin

q = r[15];

r = r << 1;

end

end

endmodule |

|

| うーん、簡単。これだけでも初心者なので結構つまづいた。最初、always文をふたつ用意してそれぞれからqを変更しようとしたところコンパイルエラーが。そこでalways文をひとつにして上のような形に落ち着いた。立ち上がり時に実行される内容にif(load)とか書いていいのか不安だったのだが、(loadの立ち上がりでイベントが発生した場合、loadはhなのかlなのか)特に問題ないようだ。 |

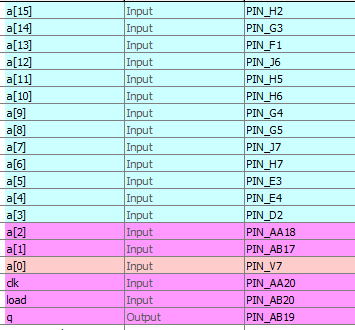

| ピンは次のように割り当てた。 |

|

|

|

| ハードウェア関連 |

|

| DE0は基本的に3.3V、SFCは5Vなのでレベル変換が必要になる。5V→3.3VにはTC74VHC125F、3.3V→5VにはTC74VHCT32AFを使った。後者はORゲートだが、一方の入力をGNDに落としておけばバッファとして使える。こいつらはデータシートどおりに繋げばよい。 |

|

|

| いざ動作確認 |

|

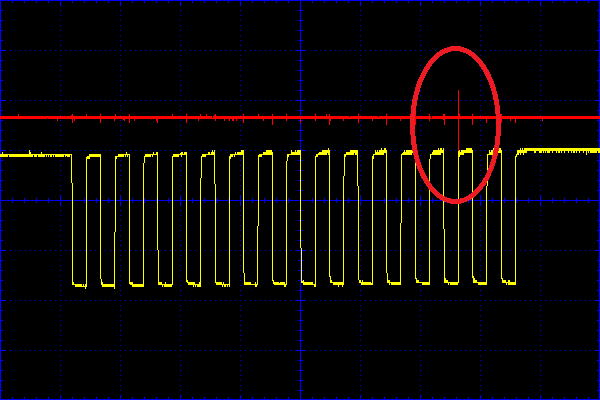

| ・・・動かない。ボタンを押してオシロの波形を見てみる。 |

|

| ・・・ん?Lowになるべきところになんかあるぞ。拡大してみよう。 |

|

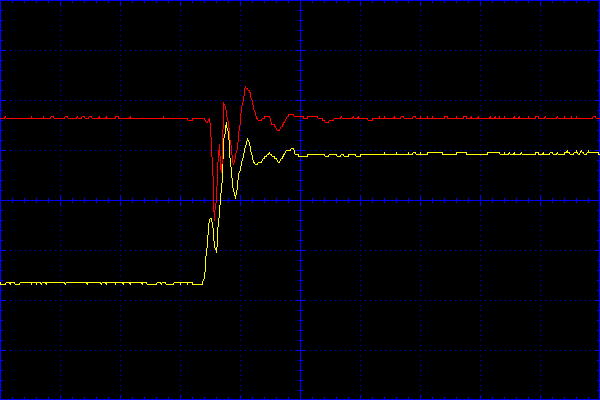

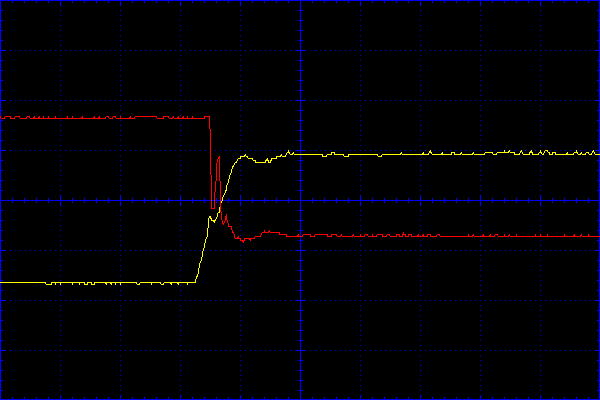

おおう!なんじゃこりゃ!何か振動しとる!信号の反射かと思ったがボタンを押していなければこのような現象は生じない。クロストークってやつか?

CLKがHighとLowの微妙なラインで揺らいでしまったためおかしな動作をしたわけだ。SFCからのクロック信号線に直列に1kΩを入れたらおさまった。 |

|

| ゲームは無事に操作できました。 |

|

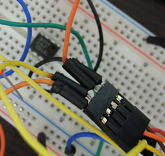

| 今回、SFCコントローラからの配線はQIコネクタにしてやった。こいつはブレッドボード用のケーブルがそのままささるので非常に便利。 |

|

| とにかく、部屋の隅で埃を被っていたDE0を久しぶりに表舞台に立たすことが出来ました。よかったよかった。 |

|

|

|

|